在通信工程领域,数据采集系统是信息获取、传输与处理的基础环节,其性能直接影响整个通信系统的效率与可靠性。随着5G、物联网、工业互联网等技术的飞速发展,对数据采集系统的速度、精度、集成度和可靠性提出了前所未有的高要求。因此,设计一种高速化与集成化的数据采集系统,已成为现代通信工程中的一项关键技术挑战。

本文旨在探讨一种面向通信工程应用的高速化与集成化数据采集系统的设计方案,涵盖系统架构、关键技术与实现路径。

一、 系统总体架构设计

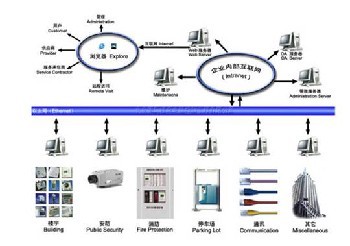

本系统采用模块化、分层化的设计思想,总体架构可分为四层:

- 传感与信号调理层:位于系统最前端,由各类传感器(如射频传感器、光传感器、温度/压力传感器等)及对应的信号调理电路组成。其核心任务是完成物理信号的感知,并将其转换为适合后续处理的电信号。为实现高速与高精度,本层需采用宽带、低噪声的传感器和高速、高精度的运放及滤波电路。

- 高速数据采集与转换层:这是系统的核心。主要包括:

- 高速模数转换器(ADC):选用采样率在GSPS(每秒千兆次采样)级别、分辨率在12位以上的高性能ADC,以满足通信信号宽带采集的需求。

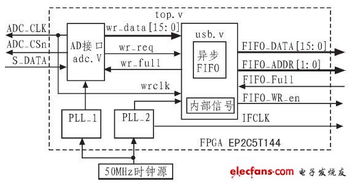

- 现场可编程门阵列(FPGA):作为采集控制与数据预处理的核心。FPGA负责产生精确的采样时钟,控制ADC的采样时序,并对ADC输出的高速原始数据进行实时预处理,如数字下变频(DDC)、滤波、抽取等,以减轻后端处理压力。

- 高速时钟与同步电路:提供低抖动、高稳定性的时钟源,并确保多通道采集间的严格同步,这对于相控阵、MIMO等通信应用至关重要。

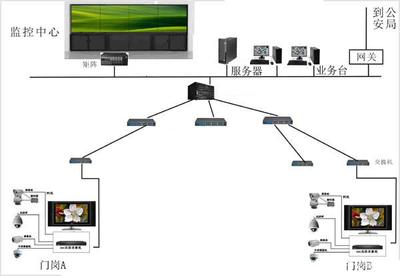

- 数据处理与传输层:主要负责数据的缓存、封装和高速传输。FPGA预处理后的数据通过高速串行接口(如PCIe Gen3/4、JESD204B/C、或10G/40G以太网)传输至主处理器(如高性能CPU或嵌入式处理器)。该层设计需确保数据传输的实时性与无阻塞,避免数据丢失。

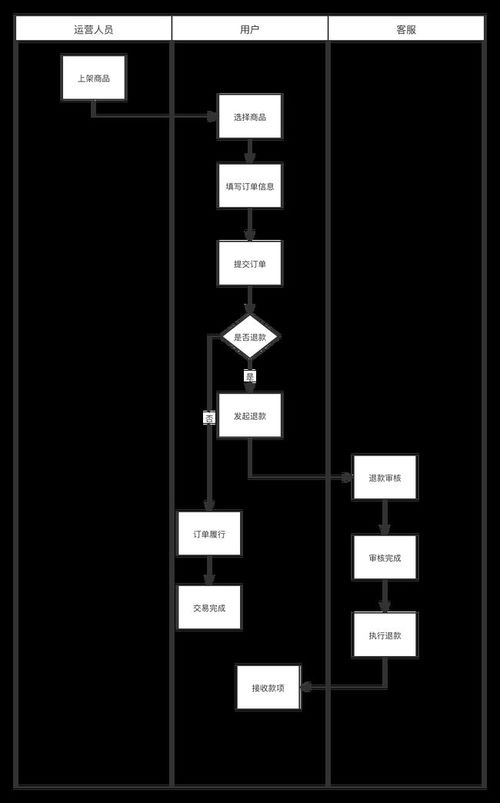

- 控制、存储与上层应用层:由主处理器、大容量存储设备(如SSD阵列)及上位机软件构成。主处理器运行嵌入式Linux或实时操作系统,负责系统的整体调度、配置管理、数据的高级处理(如频谱分析、协议解析)以及将数据存储到本地或通过网络上传至云端。上位机软件提供人机交互界面,用于系统监控、参数设置和数据分析可视化。

二、 实现高速化的关键技术

- 高速ADC与JESD204B接口技术:采用支持JESD204B/C标准的高速ADC。该标准利用高速串行链路替代传统的并行LVDS接口,极大简化了PCB布局布线,提高了通道密度和抗干扰能力,是实现多通道、超高采样率采集的关键。

- 基于FPGA的实时信号处理:利用FPGA的并行处理能力和可编程性,在数据流进入CPU之前完成大量固定算法的预处理。例如,在软件无线电(SDR)应用中,直接在FPGA内完成数字混频、滤波和重采样,仅将有效带宽内的基带数据送出,大幅降低了数据速率和对后端传输带宽的压力。

- 低抖动时钟设计与分发:使用高性能的锁相环(PLL)和压控晶体振荡器(VCXO)产生超低抖动的系统主时钟。通过专用时钟缓冲器和扇出芯片,将清洁的时钟信号分配到各个ADC和FPGA,确保采样时间的精确性,这是保证高动态范围和无杂散动态范围(SFDR)的基础。

- 高速数据传输总线:在板级互联中,优先采用PCIe Express总线,其高带宽和低延迟特性非常适合作为FPGA与CPU之间的数据通道。对于远程或分布式采集,则采用基于TCP/IP或定制UDP协议的高速以太网技术。

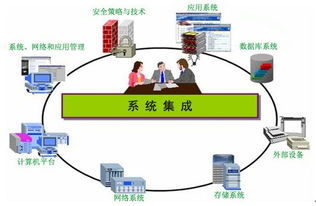

三、 实现集成化的设计策略

- 硬件集成:采用高密度、多层PCB设计,将模拟前端、高速数字电路、电源管理模块高度集成于一块板卡上。使用集成度更高的芯片(如集成ADC、时钟和数字处理的SoC FPGA),进一步缩小体积,降低功耗。对于多通道系统,可采用标准化的模块(如FMC子卡)进行扩展,实现灵活配置。

- 软件集成:构建统一的软件框架。底层驱动统一抽象为标准的API接口(如Linux IIO框架)。上层应用软件采用模块化设计,通过配置文件动态加载不同的信号处理算法插件和数据存储/上传模块,使系统能够灵活适配不同的通信测试、监测或控制系统。

- 智能与自适应集成:在系统中集成微处理器或利用FPGA的软核处理器,实现本地智能管理。系统能够根据预设规则或实时分析结果,自适应调整采集参数(如采样率、增益、中心频率),实现从“固定采集”到“智能感知与采集”的演进。

四、 系统性能评估与应用展望

设计完成的系统需从采样率、模拟带宽、信噪比(SNR)、无杂散动态范围(SFDR)、通道间隔离度、数据传输延迟与稳定性等多个维度进行严格测试。

在通信工程中,此类高速集成数据采集系统具有广阔的应用前景:

- 5G/6G基站与终端测试:用于宽带信号的发射与接收性能验证。

- 频谱监测与感知:实现大带宽范围内的实时频谱扫描与信号分析。

- 软件无线电平台:作为通用硬件平台,通过加载不同软件定义通信协议。

- 相控阵雷达与卫星通信:用于多通道射频信号的高速同步采集与波束成形处理。

- 工业物联网网关:集成多种工业协议,高速采集现场设备数据并上传。

结论

本文提出了一种面向现代通信工程的高速化与集成化数据采集系统设计方案。通过采用高速ADC、JESD204B接口、FPGA实时处理、低抖动时钟以及高速总线等关键技术,并结合硬件、软件与智能化的集成策略,该系统能够有效满足高速率、高精度、高可靠性的数据采集需求。该设计为通信设备的研发、测试、运维以及新型通信技术的探索提供了强大的硬件基础,是推动通信技术向更高带宽、更低延迟、更广连接发展的关键基础设施之一。随着芯片技术与标准协议的进步,数据采集系统将向着更高采样率、更宽带宽、更强智能和更小体积的方向持续演进。